## SwitchStar™ ATM Cell Based 8 x 8 1.2Gbps non-blocking Integrated Switching Memory

#### **Features List**

- Single chip supports an 8 x 8 port switch at 155Mbps per port

- Central Memory Architecture eliminates Head-of-Line Blocking by sharing the memory array with all ports

- ◆ Low power dissipation

- 330mW (typ.)

- Data Path Interface (DPI) provides configurable Input and Output ports; up to 8 receive and 8 transmit ports at 155Mbps

- Supports data rates up to 1.2Gbps with a 32-bit wide port configuration; 155Mbps per 4-bit port

- Can be cascaded for larger switch configurations

- Fast Input/Output port cycle times

- Expander and Concentrator function is fully supported by the Input and Output port configuration options

- 8192 cells (52 to 56 bytes each) of on-chip buffer memory capacity

- Configurable cell lengths of 52, 53, 54, 55, or 56 bytes can be independently chosen for Input and Output ports

- Byte Addition or Byte Subtraction for x4/x8 to x16/x32 conversion capability

- Internal header Cyclical Redundancy Check (CRC) and generation logic on-chip

- Header modification, pre-pend, and post-pend operations available as well as Multicasting and Broadcasting capability

- High-bandwidth control port for queue controller system block, up to 36 MHz cycle time

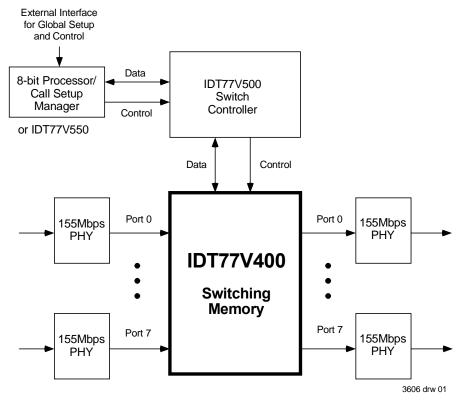

- Can be used with the companion IDT77V500 Switch Controller or custom logic for traffic management

- ◆ Industrial temperature range (-40°C to +85°C) is available

- ◆ Single +3.3V ± 300mV power supply

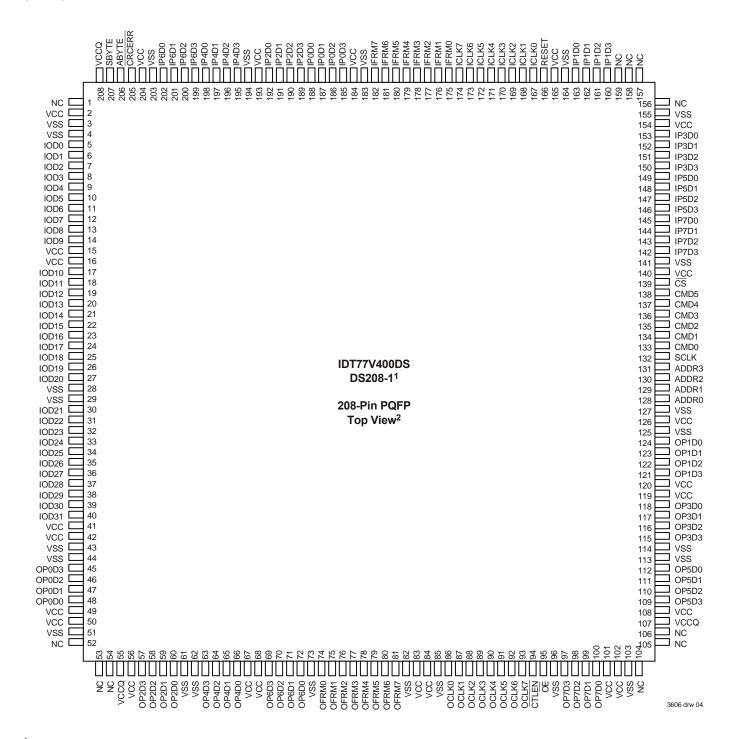

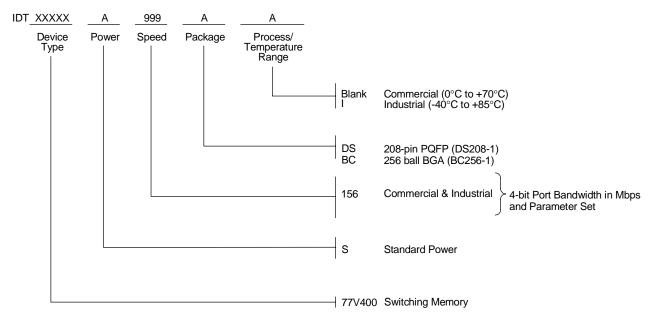

- Available in an 208-pin Plastic Quad Flat Pack (PQFP) and 256-ball BGA

#### **Block Diagram**

Figure 1 Typical 8x8 Switch Configuration using the IDT77V400 Switching Memory

SwitchStar and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

#### **Description**

The IDT77V400 ATM Cell Based Switching Memory provides the logic and memory necessary to perform high-speed buffering and switching operations on ATM cell data. A single IDT77V400 provides a cost effective switching element to implement an 8 x 8 155Mbps switch with 1.2Gbps total switching bandwidth. The user configurable data ports provide an aggregate bandwidth of 1.2Gbps for both receive and transmit functions, and the cell lengths are user programmable to up to 56 bytes.

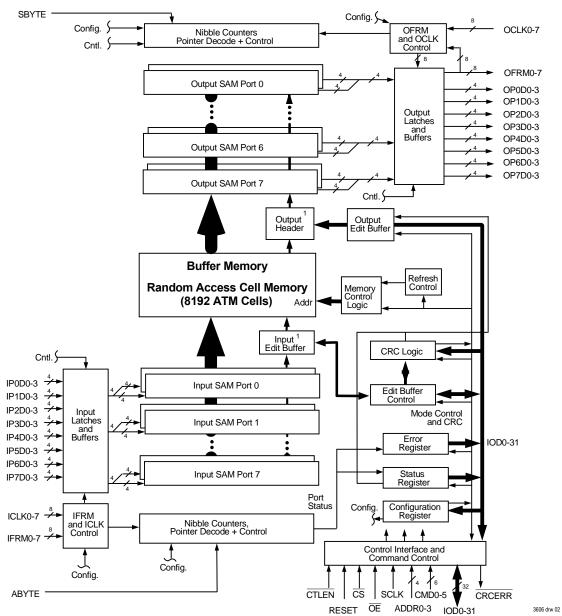

The memory provides storage for 8192 ATM cells, each of which can be as large as 56-bytes in length. The main cell memory is implemented as a Buffer Memory array, and an on-chip cell address counter keeps track of cell refresh requirements. There are also sixteen double-buffered Serial Access Memories (SAM); eight for receiving and eight for transmitting the ATM cells.

The input data ports and output data ports are configurable from eight ports of 4-bits at 155Mbps each up to one 32-bit wide port at 1.2Gbps. The sixteen data ports are asynchronous with respect to each other, and each port provides an independent data clock and cell framing signal for start of cell indication. The SAMs are double-buffered for each input and each output port to allow one cell to be transferred to or from the internal memory while that data port continues to receive or transmit a second cell. The cell framing and data clock signals implement a simple handshaking and synchronization protocol which allows multiple Switching Memories to be connected to construct larger switch arrays without requiring additional hardware.

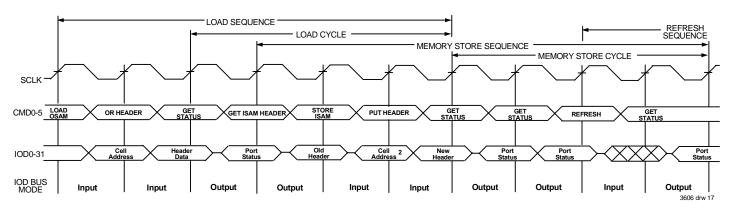

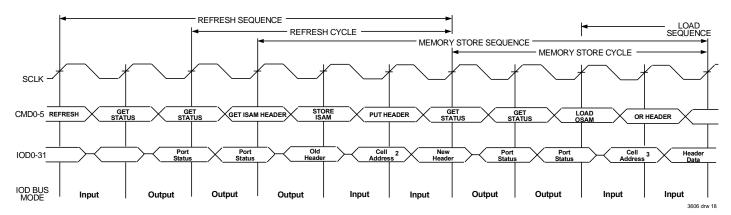

The control interface of the IDT77V400 includes a 6-bit Command Bus (CMD0-5), a 32-bit Control Data Bus (IOD0-31), a Chip Select pin (CS), a 4-bit Address field (ADDR0-3), a RESET pin, an Output Enable pin (OE), a Control Enable pin (CTLEN) and a CRCERR pin. All control operations are synchronized with respect to the System Clock (SCLK), with the exception of RESET, CTLEN, and OE, which are fully asynchronous.

The internal configuration register of the IDT77V400 can be accessed through the Control Data Bus to define the cell length and the input and output data port configurations. Internal error and status registers contain status information regarding each SAM and are accessible via the Control Data Bus (IOD0-31). Input SAM full or Output SAM empty status for all SAMs may be obtained in one access operation. Additional information regarding the reception of short or long cells and Input SAM overflow may also be obtained through the Control Data Bus.

The command set of the Switching Memory provides functions for storing cells in the shared memory, loading Output SAMs, polling the status of the data ports, retrieving and storing original or modified header bytes and pre-pend or post-pend bytes, and refreshing the cell memory. Header CRC errors are indicated by a LOW CRCERR pin; the CRC comparison byte may also be accessed via the status register, which indicates the IPort on which the error was detected. A new CRC can be generated upon storing a new header in the PHEC command. Cell headers may be modified upon cell reception at the input ports or

upon cell transmit at the output ports. User defined pre-pend and postpend bytes may also be stored, retrieved, and modified through the Control Data Bus.

The IDT77V400 has a generic control interface which supports a variety of queuing disciplines. By maintaining the memory control in an external controller, system level switching performance may be modified over time as requirements change. In normal operation, the Switching Memory port status is polled by the control function through the Control Data Bus. Upon receiving a cell, the control function can retrieve the header, check the CRC result, and store a new header if needed prior to moving the cell to the shared memory. Pre-pended or post-pended bytes may also be added or retrieved during this time. The output ports are polled at the same time to determine when to send new cells to the Output SAMs. The cell lengths of the input ports do not need to be the same as the output port cell lengths, although all input ports and output ports respectively must be configured to the same cell length.

Please refer to the SwichStar User Manual for additional feature details and implementation information.

The IDT77V400 is fully 3.3V LVTTL compatible, and is packaged in an 208-pin Plastic Quad Flatpack (PQFP) and a 256-ball BGA.

Figure 2 Functional Block Diagram

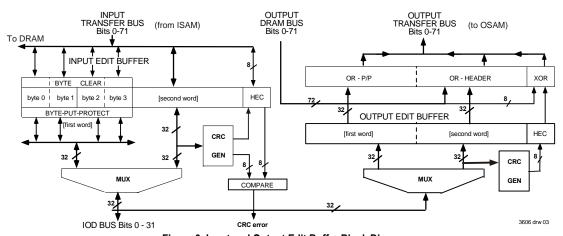

Figure 3 Input and Output Edit Buffer Block Diagram

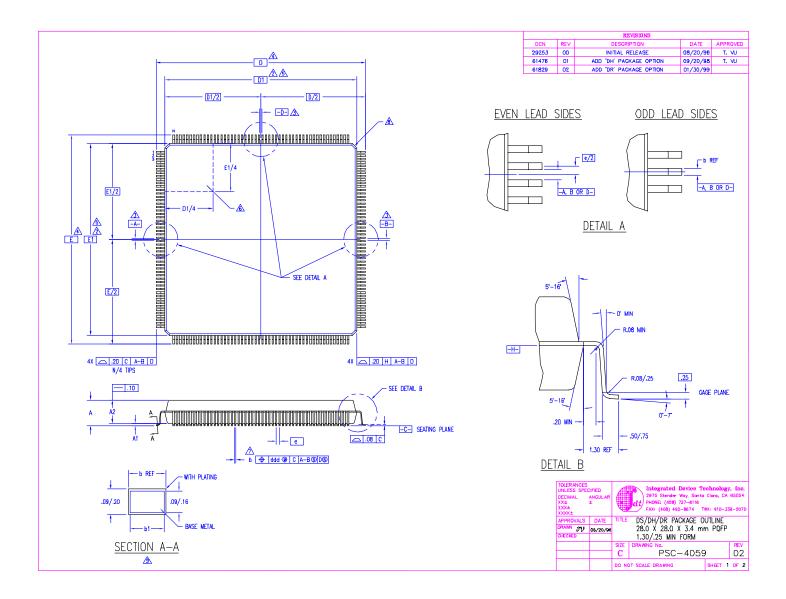

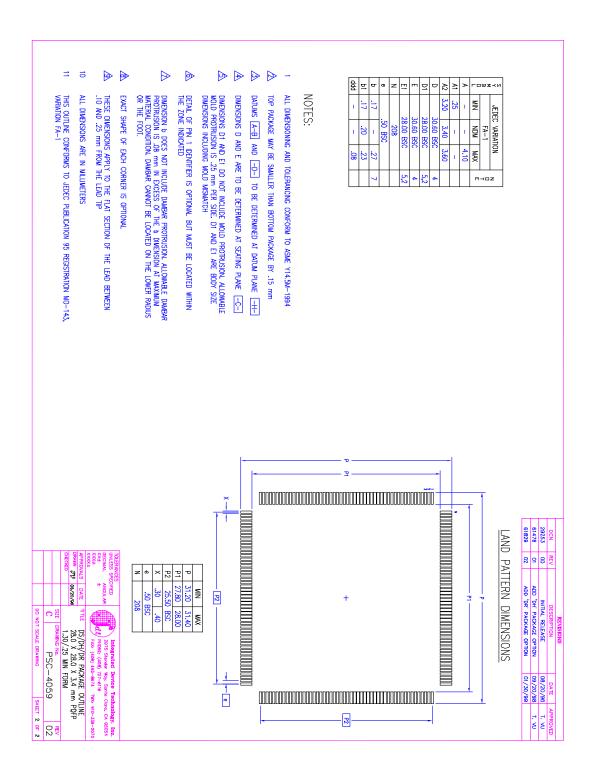

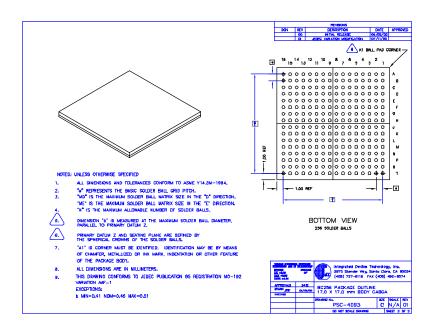

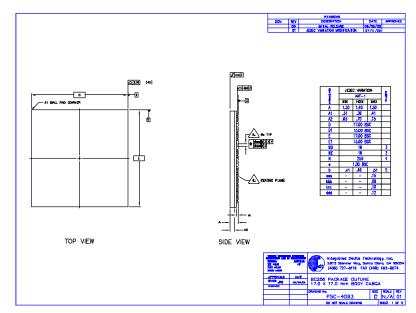

#### **Package Diagram**

All Vcc/Vccq pins must be connected to power supply. All Vss pins must be connected to ground supply. Package body is approximately 28mm x 28mm x 3.4mm.

<sup>&</sup>lt;sup>1</sup>This package code is used to reference the package diagram.

<sup>&</sup>lt;sup>2</sup>This text does not indicate orientation of the actual part marking.

## Package Diagram<sup>(1,2,3)</sup> BC256-1 BGA

| A1                | <b>A2</b>         | A3               | A4                | A5    | A6    | A7                | A8                | A9            | A10   | A11               | A12   | A13   | A14           | A15           | A16               |

|-------------------|-------------------|------------------|-------------------|-------|-------|-------------------|-------------------|---------------|-------|-------------------|-------|-------|---------------|---------------|-------------------|

| ABYTE             | C R C E R R       | IP6D1            | IP <sub>6D3</sub> | IP4D2 | IP2D1 | IPodo             | IP0D3             | IFRM4         | IFRM2 | ICLK7             | ICLK4 | ICLK1 | RESET         | IP1D1         | IP3D0             |

| B1                | B2                | B3               | B4                | B5    | B6    | B7                | B8                | B9            | B10   | B11               | B12   | B13   | B14           | B15           | B16               |

| IOD1              | SBYTE             | IP6D0            | IP <sub>6D2</sub> | IP4D1 | IP2D0 | IP2D3             | IP <sub>0D2</sub> | IFRM5         | IFRM1 | ICLK6             | ICLK3 | ICLK0 | IP1D0         | IP1D3         | IP3D1             |

| C1                | C2                | C3               | C4                | C5    | C6    | C7                | C8                | C9            | C10   | C11               | C12   | C13   | C14           | C15           | C16               |

| IOD2              | IOD3              | IOD <sub>0</sub> | IP <sub>4D0</sub> | IP4D3 | IP2D2 | IP <sub>0D1</sub> | IFRM7             | IFRM6         | IFRM3 | IFRM <sub>0</sub> | ICLK5 | ICLK2 | IP1D2         | <b>IP</b> 3D2 | IP <sub>3D3</sub> |

| D1                | D2                | D3               | D4                | D5    | D6    | D7                | D8                | D9            | D10   | D11               | D12   | D13   | D14           | D15           | D16               |

| IOD6              | IOD4              | IOD5             | VCC               | VCC   | VCC   | VCC               | Vcc               | VCC           | VCC   | VCC               | VCC   | VCC   | IP5D2         | <b>IP</b> 5D1 | IP5D0             |

| E1                | E2                | E3               | E4                | E5    | E6    | E7                | E8                | E9            | E10   | E11               | E12   | E13   | E14           | E15           | E16               |

| IOD8              | IOD7              | IOD9             | Vcc               | VCC   | Vcc   | Vss               | Vss               | Vss           | Vss   | VCC               | VCC   | VCC   | IP7D1         | IP5D3         | IP7D0             |

| F1                | F2                | F3               | F4                | F5    | F6    | F7                | F8                | F9            | F10   | F11               | F12   | F13   | F14           | F15           | F16               |

| IOD <sub>11</sub> | IOD <sub>10</sub> | IOD12            | Vcc               | Vcc   | Vss   | Vss               | Vss               | Vss           | Vss   | Vss               | VCC   | Vcc   | C S           | IP7D2         | IP7D3             |

| G1                | G2                | G3               | G4                | G5    | G6    | G7                | <sub>G8</sub>     | <sub>G9</sub> | G10   | G11               | G12   | G13   | G14           | G15           | G16               |

| IOD14             | IOD13             | IOD15            | Vcc               | Vss   | Vss   | Vss               | Vss               | Vss           | Vss   | Vss               | Vss   | VCC   | CMD3          | CMD5          | CMD4              |

| H1                | H2                | H3               | H4                | H5    | H6    | H7                | H8                | H9            | H10   | H11               | H12   | H13   | H14           | H15           | H16               |

| IOD17             | IOD16             | IOD18            | Vcc               | Vss   | Vss   | Vss               | Vss               | Vss           | Vss   | Vss               | Vss   | VCC   | CMD0          | CMD2          | CMD1              |

| J1                | J2                | J3               | J4                | J5    | J6    | J7                | <sup>J8</sup>     | <sup>J9</sup> | J10   | J11               | J12   | J13   | J14           | J15           | J16               |

| IOD20             | IOD21             | IOD19            | VCC               | Vss   | Vss   | Vss               | Vss               | Vss           | Vss   | Vss               | Vss   | Vcc   | SCLK          | ADDR2         | ADDR3             |

| K1                | K2                | K3               | K4                | K5    | K6    | K7                | K8                | K9            | K10   | K11               | K12   | K13   | K14           | K15           | K16               |

| IOD23             | IOD24             | IOD22            | Vcc               | Vss   | Vss   | Vss               | Vss               | Vss           | Vss   | Vss               | Vss   | Vcc   | ADDR0         | OP1D0         | ADDR1             |

| L1                | L2                | L3               | L4                | L5    | L6    | L7                | L8                | L9            | L10   | L11               | L12   | L13   | L14           | L15           | L16               |

| IOD26             | IOD27             | IOD25            | VCC               | Vcc   | Vss   | Vss               | Vss               | Vss           | Vss   | Vss               | VCC   | VCC   | OP1D2         | <b>OP</b> 1D3 | OP1D1             |

| M1                | M2                | M3               | M4                | M5    | M6    | M7                | M8                | M9            | M10   | M11               | M12   | M13   | M14           | M15           | м16               |

| IOD29             | IOD30             | IOD28            | VCC               | Vcc   | Vcc   | Vss               | Vss               | Vss           | Vss   | VCC               | VCC   | Vcc   | OP3D1         | OP3D2         | ОР3D0             |

| N1                | N2                | N3               | N4                | N5    | N6    | N7                | N8                | N9            | N10   | N11               | N12   | N13   | N14           | N15           | N16               |

| OP0D3             | OP0D2             | IOD31            | VCC               | VCC   | VCC   | VCC               | Vcc               | VCC           | VCC   | VCC               | VCC   | VCC   | OP5D0         | OP5D1         | OP3D3             |

| P1                | P2                | P3               | P4                | P5    | P6    | P7                | P8                | P9            | P10   | P11               | P12   | P13   | P14           | P15           | P16               |

| OP0D1             | OP0D0             | NC               | OP2D0             | OP4D0 | OP6D1 | OFRM1             | OFRM4             | OFRM5         | OCLK0 | OCLK3             | OCLK6 | O E   | NC            | OP5D3         | OP5D2             |

| R1                | R2                | R3               | R4                | R5    | R6    | R7                | R8                | R9            | R10   | R11               | R12   | R13   | R14           | R15           | R16               |

| NC                | NC                | OP2D3            | OP2D1             | OP4D2 | OP6D3 | OP6D0             | OFRM2             | OFRM7         | OCLK2 | OCLK5             | CTLEN | OP7D3 | <b>OP</b> 7D0 | NC            | NC                |

| T1                | T2                | T3               | T4                | T5    | T6    | T7                | T8                | T9            | T10   | T11               | T12   | T13   | T14           | T15           | T16               |

| NC                | NC                | OP2D2            | OP4D3             | OP4D1 | OP6D2 | OFRMo             | OFRM3             | OFRM6         | OCLK1 | OCLK4             | OCLK7 | OP7D2 | OP7D1         | NC            | NC                |

3606 drw 04a

**Note:** 1. All Vcc pins must be connected to power supply.

- 2. All Vss pins must be connected to ground supply.

- 3. Package body is approximately 17mm x 17mm x 1.4mm.

## Pin Description - PQFP Package

| Pin Number                                                                      | Symbol        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 132                                                                             | SCLK          | I    | System clock: All bus control signals (CMD0-5, $\overline{CS}$ , IOD0-31, $\overline{CRCERR}$ ) except $\overline{OE}$ are synchronous with respect to SCLK. Control commands are registered on the positive edge of SCLK. The SCLK period must be less than or equal to 200ns during normal operation. Data Port signals are asynchronous with respect to SCLK.                                                                                                                                                                                                                                                                                                                                  |

| 139                                                                             | CS            | I    | Chip Select: Synchronous input which must be LOW at the rising edge of SCLK to enable the Command Bus CMD0-5. Instructions are a NOP when $\overline{\text{CS}}$ is HIGH at the SCLK positive edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 133-138                                                                         | CMD0-5        | I    | Command Bus: Synchronized to SCLK, instructions to be executed by the memory are transferred across this 6-bit bus. CMD5 is the MSb of the Command Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 95                                                                              | ŌĒ            | I    | Output Enable: Asynchronous input that enables all outputs when asserted LOW. All outputs are High-Z when $\overline{\text{OE}}$ is HIGH. IOD0-31 and CRCERR may also be set to High-Z by a HIGH CTLEN bit in the configuration register or a HIGH CTLEN pin.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 166                                                                             | RESET         | I    | Reset: When asserted HIGH, the signal asynchronously allows the initialization of the registers and internal signals of the IDT77V400. RESET should be asserted HIGH and $\overline{\text{OE}}$ should be held HIGH upon power-up for the external controller to execute the initialization and insure proper system operation.                                                                                                                                                                                                                                                                                                                                                                   |

| 128-131                                                                         | ADDR0-3       | I    | Chip Address: All ADDR inputs must OR the address in the configuration register bits 26-29 and then must match 10D13-16 one cycle after the Store or Load command for selection to allow a Store or Load memory cycle to be executed (full flag is cleared regardless of match, and empty must match before clear). ADDR3 is the MSb of the device address bits.                                                                                                                                                                                                                                                                                                                                  |

| 5-14, 17-27, 30-40                                                              | IOD0-31       | I/O  | Control Data Bus: Synchronous with SCLK. Used for external data transfer for the header pre/post-pend bytes, configuration register error and status registers, and the cell memory address. IOD31 is the MSb of the Control Data Bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 205                                                                             | CRCERR        | 0    | Cyclical Redundancy Check Error: Synchronous output on the rising edge of SCLK. CRCERR asserted LOW after a Header with CRC operation indicates that a CRC error has occurred on the previous header.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 167-174                                                                         | ICLK0-7       | I    | Input Port Clock: Synchronizes the input data IPxD(0-3) and IFRMx signal associated with the input data port on the positive clock edge. Each ICLKx is independent of the other seven ICLKs and SCLK. The ICLKs used are determined by the configuration register initialization (see Port Configuration Code Table). The inputting of a cell may be halted by stopping ICLKx.                                                                                                                                                                                                                                                                                                                    |

| 175-182                                                                         | IFRM0-7       | I    | Input Frame: Synchronous input registered on the rising edge of ICLKx. When asserted HIGH this signal denotes the beginning of an input cell for the associated input port. IFRMs used are determined by the configuration register during initialization (see Port Configuration Code Table).                                                                                                                                                                                                                                                                                                                                                                                                    |

| 185-188, 160-163,<br>189-192, 150-153,<br>195-198, 146-149,<br>199-202, 142-145 | IP(0-7)D(0-3) | I    | Input Data: Eight 4-bit input ports. Synchronous with the rising edge of ICLK for the associated data port. IPxD(0-3) can be assigned to different ICLKs and IFRMs via the configuration register during initialization. The ports may be combined in groups to increase bandwidth by factors of 155Mbps (see Port Configuration Code Table). IPxD3 is the MSb of the nibble. Example: IP0D3 is the MSb for port 0.                                                                                                                                                                                                                                                                               |

| 86-93                                                                           | OCLK0-7       | I    | Output Clock: Synchronizes the output data OPxD(0-3) and OFRMx signal associated output data port on the positive clock edge. Each OCLK is independent of the other seven OCLKs and SCLK. OCLKs used are determined by the port configuration register during initialization (see Port Configuration Code Table). The transmission of a cell may be halted by stopping OCLKx.                                                                                                                                                                                                                                                                                                                     |

| 74-81                                                                           | OFRM0-7       | 1/0  | Output Frame: Synchronous output on the rising edge of OCLK. The 77V400 marks the beginning of an output cell by taking OFRM HIGH on the rising edge of OCLK. The output SAM nibble counter loads the start byte address from the configuration register when a HIGH signal is sensed at the OFRM pin, thus re-synchronizing other chips connected to the OFRM bus. OFRM is asserted HIGH one OCLK cycle prior to the first nibble of the cell being output from the IDT77V400. OFRMs used are determined by the configuration register initialization (see Port Configuration Code Table). During cell bus operations, the OFRM1-7 are redefined as CBUS1-7 for arbitration (there is no CBUS0). |

| 45-48, 121-124, 57-<br>60, 115-118, 63-66,<br>109-112, 69-72, 97-<br>100        | OP(0-7)D(0-3) | 0    | Output Data: Eight 4-bit output ports. Synchronous with the rising edge of OCLK for the associated data port. OPxD(0-3) can be assigned to different OCLKs and OFRMs via the configuration register. The 4 bit ports may be combined in groups to increase the bandwidth by factors of 155Mbps (see Port Configuration Code Table). OPxD3 is the MSb of the nibble. Example: IP0D3 is the MSb for port 0.                                                                                                                                                                                                                                                                                         |

## IDT77V400

| Pin Number                                                                                                    | Symbol | Туре  | Description                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 94                                                                                                            | CTLEN  | I     | Control Enable: When asserted LOW, with OE LOW and the CTLEN bit set LOW in the configuration register, this pin asynchronously enables all Control interface outputs. If CTLEN is HIGH all control interface outputs will be High-Z.                                                                                                                           |

| 206                                                                                                           | ABYTE  | I     | Add Byte to Input cell: Asynchronous DC signal. If an input port is in a 4-bit or 8-bit DPI mode and ABYTE is asserted HIGH, a dummy byte will be inserted in the ninth byte position (after the HEC byte) to support systems requiring a byte between the last header byte and the payload (otherwise ignored). Not intended for dynamic cycling or operation. |

| 207                                                                                                           | SBYTE  | I     | Subtract Byte to Output cell: Asynchronous DC signal. When and SBYTE is asserted HIGH, the dummy byte in the ninth byte position (after the HEC byte) will be removed prior to transmission to support output port 4-bit and 8-bit DPI modes (otherwise ignored). Not intended for dynamic cycling or operation.                                                |

| 1, 52-54, 104-06,<br>156-59                                                                                   | NC     | _     | No Connect                                                                                                                                                                                                                                                                                                                                                      |

| 2, 15-16, 41-42, 49-<br>50, 56, 67-68, 83-84,<br>101-02, 108, 119-20,<br>126, 140, 154, 165,<br>184, 193, 204 |        | Power | Power Supply (+3.3V ± 300mV)                                                                                                                                                                                                                                                                                                                                    |

| 55, 107, 208                                                                                                  | VCCQ   | Power | Output Power Supply (+3.3 ± 300mV)                                                                                                                                                                                                                                                                                                                              |

| 3-4, 28-29, 43-44,<br>51, 61-62, 73, 82, 85,<br>96, 103, 113-14,<br>125, 127, 141, 155,<br>164, 183, 194, 203 | VSS    | Power | Ground                                                                                                                                                                                                                                                                                                                                                          |

## Pin Description - BGA Package

| Pin Number                                                                  | Symbol  | Туре | Description                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J14                                                                         | SCLK    | I    | System clock: All bus control signals (CMD0-5, CS, IOD0-31, CRCERR) except OE are synchronous with respect to SCLK. Control commands are registered on the positive edge of SCLK. The SCLK period must be less than or equal to 200ns during normal operation. Data Port signals are asynchronous with respect to SCLK.                                          |

| F14                                                                         | CS      | I    | Chip Select: Synchronous input which must be LOW at the rising edge of SCLK to enable the Command Bus CMD0-5. Instructions are a NOP when CS is HIGH at the SCLK positive edge.                                                                                                                                                                                  |

| G14-16, H14-16                                                              | CMD0-5  | I    | Command Bus: Synchronized to SCLK, instructions to be executed by the memory are transferred across this 6-bit bus. CMD5 is the MSb of the Command Bus.                                                                                                                                                                                                          |

| P13                                                                         | ŌĒ      | I    | Output Enable: Asynchronous input that enables all outputs when asserted LOW. All outputs are High-Z when $\overline{OE}$ is HIGH. IOD0-31 and $\overline{CRCERR}$ may also be set to High-Z by a HIGH $\overline{CTLEN}$ bit in the configuration register or a HIGH $\overline{CTLEN}$ pin.                                                                    |

| A14                                                                         | RESET   | I    | Reset: When asserted HIGH, the signal asynchronousl <u>v</u> allows the initialization of the registers and internal signals of the IDT77V400. RESET should be asserted HIGH and OE should be held HIGH upon power-up for the external controller to execute the initialization and insure proper system operation.                                              |

| J15-16, K14, K16                                                            | ADDR0-3 | 1    | Chip Address: All ADDR inputs must OR the address in the configuration register bits 26-29 and then must match 10D13-16 one cycle after the Store or Load command for selection to allow a Store or Load memory cycle to be executed (full flag is cleared regardless of match, and empty must match before clear). ADDR3 is the MSb of the device address bits. |

| B1, C1-3, D1-3,E1-3,<br>F1-3, G1-3, H1-3,<br>J1-3, K1-3, L1-3, M1-<br>3, N3 |         | I/O  | Control Data Bus: Synchronous with SCLK. Used for external data transfer for the header pre/post-pend bytes, configuration register error and status registers, and the cell memory address. IOD31 is the MSb of the Control Data Bus.                                                                                                                           |

| A2                                                                          | CRCERR  | 0    | Cyclical Redundancy Check Error: Synchronous output on the rising edge of SCLK. CRCERR asserted LOW after a Header with CRC operation indicates that a CRC error has occurred on the previous header.                                                                                                                                                            |

## IDT77V400

| Pin Number                                                                                                               | Symbol        | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A11-13, B11-13,<br>C12-13                                                                                                | ICLK0-7       | I     | Input Port Clock: Synchronizes the input data IPxD(0-3) and IFRMx signal associated with the input data port on the positive clock edge. Each ICLKx is independent of the other seven ICLKs and SCLK. The ICLKs used are determined by the configuration register initialization (see Port Configuration Code Table). The inputting of a cell may be halted by stopping ICLKx.                                                                                                                                                                                                                                                                                                                    |

| A9-10, B9-10,C8-11                                                                                                       | IFRM0-7       | I     | Input Frame: Synchronous input registered on the rising edge of ICLKx. When asserted HIGH this signal denotes the beginning of an input cell for the associated input port. IFRMs used are determined by the configuration register during initialization (see Port Configuration Code Table).                                                                                                                                                                                                                                                                                                                                                                                                    |

| A3-8, A15-16, B3-8,<br>B14-16, C4-7,<br>C14-16, D14-16,<br>E14-16, F15-16                                                | IP(0-7)D(0-3) | I     | Input Data: Eight 4-bit input ports. Synchronous with the rising edge of ICLK for the associated data port. IPxD(0-3) can be assigned to different ICLKs and IFRMs via the configuration register during initialization. The ports may be combined in groups to increase bandwidth by factors of 155Mbps (see Port Configuration Code Table). IPxD3 is the MSb of the nibble. Example: IP0D3 is the MSb for port 0.                                                                                                                                                                                                                                                                               |

| P10-12, R10-11,<br>T10-12                                                                                                | OCLK0-7       | I     | Output Clock: Synchronizes the output data OPxD(0-3) and OFRMx signal associated output data port on the positive clock edge. Each OCLK is independent of the other seven OCLKs and SCLK. OCLKs used are determined by the port configuration register during initialization (see Port Configuration Code Table). The transmission of a cell may be halted by stopping oclkx.                                                                                                                                                                                                                                                                                                                     |

| P7-9, R8-9, T7-9                                                                                                         | OFRM0-7       | I/O   | Output Frame: Synchronous output on the rising edge of OCLK. The 77V400 marks the beginning of an output cell by taking OFRM HIGH on the rising edge of OCLK. The output SAM nibble counter loads the start byte address from the configuration register when a HIGH signal is sensed at the OFRM pin, thus re-synchronizing other chips connected to the OFRM bus. OFRM is asserted HIGH one OCLK cycle prior to the first nibble of the cell being output from the IDT77V400. OFRMs used are determined by the configuration register initialization (see Port Configuration Code Table). During cell bus operations, the OFRM1-7 are redefined as CBUS1-7 for arbitration (there is no CBUS0). |

| K15, L14-16, M14-16,<br>N1-2, N14-16, P1-2,<br>P4-6, P15-16, R3-7,<br>R13-14, T3-6,T13-14                                | OP(0-7)D(0-3) | 0     | Output Data: Eight 4-bit output ports. Synchronous with the rising edge of OCLK for the associated data port. OPxD(0-3) can be assigned to different OCLKs and OFRMs via the configuration register. The 4 bit ports may be combined in groups to increase the bandwidth by factors of 155Mbps (see Port Configuration Code Table). OPxD3 is the MSb of the nibble. Example: IP0D3 is the MSb for port 0.                                                                                                                                                                                                                                                                                         |

| R12                                                                                                                      | CTLEN         | I     | Control Enable: When asserted LOW, with OE LOW and the CTLEN bit set LOW in the configuration register, this pin asynchronously enables all Control interface outputs. If CTLEN is HIGH all control interface outputs will be High-Z.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A1                                                                                                                       | ABYTE         | I     | Add Byte to Input cell: Asynchronous DC signal. If an input port is in a 4-bit or 8-bit DPI mode and ABYTE is asserted HIGH, a dummy byte will be inserted in the ninth byte position (after the HEC byte) to support systems requiring a byte between the last header byte and the payload (otherwise ignored). Not intended for dynamic cycling or operation.                                                                                                                                                                                                                                                                                                                                   |

| B2                                                                                                                       | SBYTE         | I     | Subtract Byte to Output cell: Asynchronous DC signal. When and SBYTE is asserted HIGH, the dummy byte in the ninth byte position (after the HEC byte) will be removed prior to transmission to support output port 4-bit and 8-bit DPI modes (otherwise ignored). Not intended for dynamic cycling or operation.                                                                                                                                                                                                                                                                                                                                                                                  |

| P3, P14, R1-2, R15-<br>16, T1-2, T15-16                                                                                  | NC            | _     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D4-13, E4-6, E11-13,<br>F4-5, F12-13, G4,<br>G13, H4, H13, J4,<br>J13, K4, K13, L4-5,<br>L12-13, M4-6, M11-<br>13, N4-13 | VCC           | Power | Power Supply (+3.3V +300mV)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| E7-10, F6-11, G5-12,<br>H5-12, J5-12, K5-12,<br>L6-11, M7-10                                                             |               | Power | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## **Absolute Maximum Ratings**

| Symbol             | Rating <sup>1</sup>                  | Commercial   | Unit |

|--------------------|--------------------------------------|--------------|------|

| VTERM <sup>2</sup> | Terminal Voltage with Respect to Vss | -0.5 to +3.9 | V    |

| TBIAS              | Temperature Under Bias               | -55 to +125  | °C   |

| Тѕтс               | Storage Temperature                  | -55 to +125  | °C   |

| Іоит               | DC Output Current                    | 50           | mA   |

<sup>1.</sup> Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Maximum Operating Temperature and Supply Voltage**

| Grade      | Ambient Temperature <sup>1</sup> | GND | Vcc                              |

|------------|----------------------------------|-----|----------------------------------|

| Commercial | 0°C to +70°C                     | 0V  | $3.3\text{V} \pm 300\text{mV}$   |

| Industrial | -40°C to +85°C                   | 0V  | $3.3 \text{V} \pm 300 \text{mV}$ |

<sup>1.</sup> This is the parameter TA.

### Capacitance (TA = +25°C, f = 1.0MHz) PQFP ONLY

| Symbol            | Parameter <sup>1</sup> | Conditions <sup>2</sup> | Max. | Unit |

|-------------------|------------------------|-------------------------|------|------|

| CIN               | Input Capacitance      | VIN = 3dV               | 9    | pF   |

| Cout <sup>3</sup> | Output Capacitance     | Vout = 3dV              | 10   | pF   |

<sup>&</sup>lt;sup>1</sup> These parameters are determined by device characterization, but are not production tested.

## **Recommended DC Operating Conditions**

| Symbol | Parameter          | Min.       | Тур. | Max.                      | Unit |

|--------|--------------------|------------|------|---------------------------|------|

| Vcc    | Supply Voltage     | 3.0        | 3.3  | 3.6                       | V    |

| Vss    | Ground             | 0          | 0    | 0                         | V    |

| VIH    | Input High Voltage | 2.0        | _    | Vcc + 0.3 <sup>1, 2</sup> | V    |

| VIL    | Input Low Voltage  | $-0.3^{3}$ | _    | 0.8                       | V    |

<sup>1.</sup> VIL ≥ -1.5V for pulse width less than 10ns.

<sup>2.</sup> VTERM must not exceed Vcc + 0.3V for more than 25% of the cycle time or 10ns maximum, and is limited to ≤ 20mA for the period of VTERM ≥ Vcc + 0.3V.

$<sup>^2</sup>$  3dV references the interpolated capacitance when the input and output switch from 0V to 3V or from 3V to 0V.

<sup>3.</sup> Cout also references Ci/o

<sup>&</sup>lt;sup>2.</sup> VTERM must not exceed Vcc + 0.3V or Vss – 0.3V.

$<sup>^3</sup>$ . VTERM must not exceed Vcc + 0.3V for more than 25% of the cycle time or 10ns maximum, and is limited to  $\leq$  20mA for the period of VTERM  $\geq$  Vcc + 0.3V.

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (Vcc = 3.3V $\pm$ 0.3V)

|        |                        |                                                   | 77V400S |      |      |

|--------|------------------------|---------------------------------------------------|---------|------|------|

| Symbol | Parameter              | Test Conditions                                   | Min.    | Max. | Unit |

| lu     | Input Leakage Current  | Vcc = 3.6V, Vin = 0V to Vcc                       |         | 10   | μA   |

| llo    | Output Leakage Current | CS = VIH, VOUT = 0V to VCC, OE = VIH, CTLEN = VIH |         | 10   | μΑ   |

| VoL    | Output Low Voltage     | IOL = +4mA                                        |         | 0.4  | ٧    |

| Voн    | Output High Voltage    | IOH = -4mA                                        | 2.4     |      | ٧    |

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range (Vcc = 3.3V $\pm$ 0.3V)

|        |                   |                                                                                           | 77V400 | S156DSI | 77V400S156DS |      |      |

|--------|-------------------|-------------------------------------------------------------------------------------------|--------|---------|--------------|------|------|

| Symbol | Parameter         | Test Conditions                                                                           | Тур.   | Max.    | Тур.         | Max. | Unit |

| Icc    | Operating Current | Vcc = 3.6V, CS = VIL, OE = VIH,<br>CTLEN = VIH, RESET = VIL or VIH, f = fmax <sup>1</sup> | 100    | 180     | 100          | 160  | mA   |

<sup>1.</sup> At f = fmax SCLK, ICLK, and OCLK are cycling at their maximum frequency and all inputs are cycling at 1/tCYC1, using AC input levels of VSS to 3.0V.

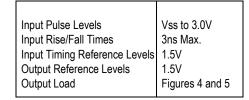

#### **AC Test Conditions**

Figure 4 AC Output Test Load

Figure 5 Output Test Load (for High-Impedance parameters)

\* Including scope and jig.

# AC Electrical Characteristics Over the Operating Temperature Range (Read and Write Cycle Timing) ( $Vcc = 3.3V \pm 0.3V$ )

|        |                            | 77V400 |      |      |

|--------|----------------------------|--------|------|------|

| Symbol | Parameter                  | Min.   | Max. | Unit |

| tcyc   | System Clock Cycle Time    | 25     | _    | ns   |

| tCH    | System Clock High Time     | 10     | _    | ns   |

| tCL    | System Clock Low Time      | 10     | _    | ns   |

| tR     | Clock Rise Time            | _      | 3    | ns   |

| tF     | Clock Fall Time            | _      | 3    | ns   |

| tsc    | CS Setup Time to SCLK High | 4      | _    | ns   |

|                    |                                          | 77V400S156 Com'l & Ind |      |      |  |  |

|--------------------|------------------------------------------|------------------------|------|------|--|--|

| Symbol             | Parameter                                | Min.                   | Max. | Unit |  |  |

| tHC                | CS Hold Time after SCLK High             | 1                      | _    | ns   |  |  |

| tSCM               | CMD Setup Time to SCLK High              | 4                      | _    | ns   |  |  |

| tHCM               | CMD Hold Time after SCLK High            | 1                      | _    | ns   |  |  |

| tsio               | IOD Setup Time to SCLK High              | 4                      | _    | ns   |  |  |

| tHIO               | IOD Hold Time after SCLK High            | 1                      | _    | ns   |  |  |

| tCDIO              | SCLK to IOD Valid                        | _                      | 18   | ns   |  |  |

| tDCIO              | IOD Output Hold after SCLK High          | 2                      | _    | ns   |  |  |

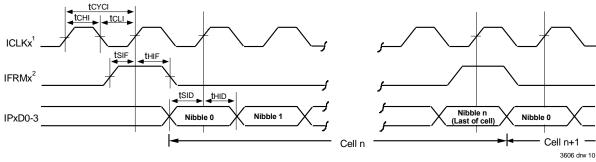

| tCYCI <sup>1</sup> | ICLK Cycle Time                          | 23                     | _    | ns   |  |  |

| tCHI               | ICLK High Time                           | 9                      | _    | ns   |  |  |

| tCLI               | ICLK Low Time                            | 9                      | _    | ns   |  |  |

| tsif               | IFRM Setup Time to ICLK High             | 4                      | _    | ns   |  |  |

| tHIF               | IFRM Hold Time after ICLK High           | 1                      | _    | ns   |  |  |

| tSID               | ID Setup Time to ICLK High               | 4                      | _    | ns   |  |  |

| tHID               | ID Hold Time after ICLK High             | 1                      | _    | ns   |  |  |

| tOE                | OE Low to Data Valid                     | _                      | 15   | ns   |  |  |

| tOHZ               | OE High to Output High-Z <sup>2</sup>    | _                      | 15   | ns   |  |  |

| tOLZ               | OE Low to Output Low-Z <sup>2</sup>      | 2                      | _    | ns   |  |  |

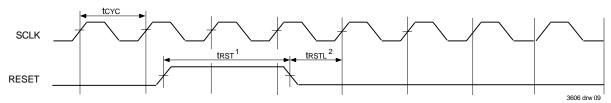

| tRST               | RESET High Pulse Width <sup>3</sup>      | 20                     | _    | ns   |  |  |

| tRSTL              | RESET Low to SCLK High                   | 10                     | _    | ns   |  |  |

| tCTEN              | CTLEN Low to Data Valid                  | _                      | 15   | ns   |  |  |

| tCTHZ              | CTLEN High to Output High-Z <sup>2</sup> | _                      | 15   | ns   |  |  |

| tCTLZ              | CTLEN Low to Output Low-Z <sup>2</sup>   | 2                      | _    | ns   |  |  |

| tCDCR              | SCLK to CRCERR Valid (1 cycle delay)     | _                      | 18   | ns   |  |  |

| tDCCR              | CRCERR Output Hold after SCLK High       | 2                      | _    | ns   |  |  |

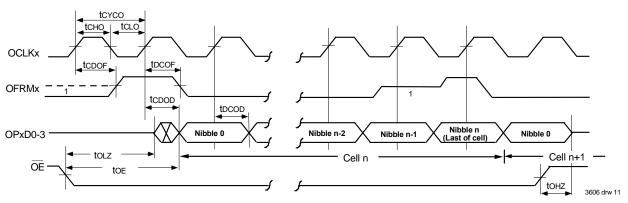

| tcyco              | OCLK Cycle                               | 23                     | _    | ns   |  |  |

| tCHO               | OCLK High Time                           | 9                      | _    | ns   |  |  |

| tCLO               | OCLK Low Time                            | 9                      | _    | ns   |  |  |

| tsof               | OFRM Setup Time to OCLK High             | 4                      | _    | ns   |  |  |

| tHOF               | OFRM Hold Time after OCLK High           | 1                      | _    | ns   |  |  |

| tCDOF              | OCLK to OFRM Valid                       | _                      | 18   | ns   |  |  |

| tCDOF              | OFRM Output Hold after OCLK High         | 2                      | _    | ns   |  |  |

| tCDOD              | OCLK to OPxD Valid                       | _                      | 18   | ns   |  |  |

| tDCOD              | OD Output Hold after OCLK High           | 2                      | _    | ns   |  |  |

| tCKHZ              | SCLK High to Output High-Z <sup>2</sup>  | _                      | 15   | ns   |  |  |

| tCKLZ              | SCLK High to Output Low-Z <sup>2</sup>   | 2                      | _    | ns   |  |  |

<sup>&</sup>lt;sup>1</sup> ICLK frequency must not exceed SCLK frequency.

<sup>2.</sup> Transition is measured +/-200mV from Low or High impedance voltage with the Output Test Load (Figure 2). This parameter is guaranteed by device characterization, but is not production tested

<sup>3.</sup> Although RESET is an asynchronous function, it must be centered around the SCLK so that it will be Low 10ns prior to the next SCLK rising edge to prevent initiating another Reset operation.

#### **Basic Functional Description**

Input data is received by the Switching Memory via the four-bit input data ports (IPxD). Each input port is configured as a double buffer with SRAM storage for two complete ATM cells. Each input port also has an independent input clock, (ICLK) and an input framing signal (IFRM).

The external controller may poll the internal status register through the Control Data Bus (IOD Bus) to determine if any of the eight input SAMs (ISAMx) are full and any of the eight Output SAMs (OSAMx) are empty. The status register accessed through the IOD Bus also provides ISAM error status information. If an error is detected for any of the ISAMs, the error register can then be read through the IOD Bus to further determine the presence of short or long cells or SAM overflow. OFRM may also be used to monitor OSAM status.

Upon a Store command, data from the selected ISAM is transferred to the cell memory at the location selected by the controller on the IOD Bus. Similarly, on a Load command data from the specified cell memory location is transferred to the OSAMx specified by the controller on the IOD Bus. The output ports are also individually double buffered and each output port can hold up to two complete ATM cells. A cell output ready signals the status register to allow the loading of the second buffer to begin while the first buffer begins to transmit via the 4-bit output port. Each output port has an independent clock (OCLKx) and output framing signal (OFRMx).

Once a cell has been received in the ISAM, the header bytes and the pre/post-pend bytes, if enabled, may be examined and modified via the IOD bus. The CRC byte may also be modified, although it is modified internally to the switching memory and is not read on the IOD Bus. The IOD Bus is also used to set the internal configuration register at initialization, determining the input and output cell length and the input and output port configurations. The input edit buffer provides the means to modify the cell header or pre/post-pend data of a cell in the ISAM before storing the cell in the Memory portion of the IDT77V400. The command selected (GHE or GPE, for example) will determine which bits are transferred to the control logic across the IOD bus. Two features are included to eliminate the need for an extra step in the edit sequences of the input edit buffer. A Byte Protect function, which prevents a PUT instruction from changing any protected bytes stored in the input edit buffer, and a Clear Byte function, which clears bytes in the input edit buffer in preparation for ORing at the output, are described in the Input Ports section of this data sheet. See the Input and Output Edit Buffer Block Diagram for additional details of the functionality and data path of this circuitry.

The output edit buffer provides a means to modify the cell contents at the last possible moment prior to transmission of a cell out an output port. The output edit buffer provides data to an OR function between the Buffer Memory and the OSAMs, allowing the IOD bus to set selected bits in the cell header and pre/post pend data immediately before transmission.

The following basic functional description is divided into three sections—the control interface, the input ports, and the output ports. For clarity we will use an 8x8 Switching Memory configuration, with each

port being 4-bits wide. Higher port bandwidth can be obtained by combining multiple 4-bit wide ports into 8, 16, or 32-bit wide ports during device initialization and configuration (see Configuration Codes Table).

#### **Control Interface**

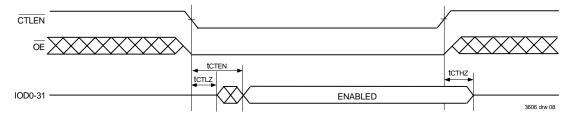

The control interface consists of 48 pins. The 32-bit control data bus (IOD0-31) is used to transfer address, data, and header information. The 6-bit command bus (CMD0-5) is used when  $\overline{\text{CS}}$  is LOW to issue commands to the Switching Memory. When  $\overline{CS}$  is HIGH, all issued commands become invalid (no operation is performed) (see the Control Interface Command Table for a listing of commands). The CRCERR output pin indicates that a CRC error has occurred on the last header when asserted LOW. The asynchronous OE input pin is the master output enable for all outputs; all output drivers will be in a high-impedance state when OE is driven HIGH. Upon power-up initialization the OE pin should be held HIGH and the RESET pin should be asserted HIGH to allow proper device initialization by the controller. The asynchronous CTLEN input pin controls the Control Interface outputs. When the CTLEN pin is LOW, the OE pin is LOW, and the CTLEN bit of the configuration register is LOW, the Control Interface outputs are enabled. If the CTLEN pin or the CTLEN bit of the configuration register is HIGH, all control Interface outputs will be in the High-Z state (see Control Enable Timing Waveform). The ADDR0-3 pins are used in conjunction with the configuration register to selectively enable Switching Memories that are sharing a control bus. All inputs and outputs of the control interface, with the exception of OE, RESET, and ADDR0-3 are synchronous with the system clock input (SCLK).

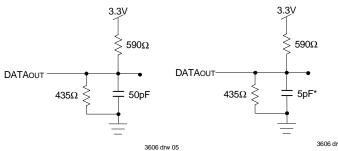

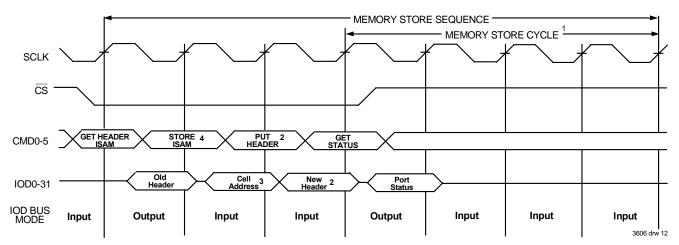

As shown in the Control Interface Timing Waveform, the control interface provides access to five internal registers — the configuration register, the status register, the error register, the input edit buffers, and the output edit buffers. The control interface is implemented as a pipeline. Commands are registered on the rising edge of SCLK, and in general, the Switching Memory either expects data or will output data on IOD0-31 on the subsequent SCLK rising edge. The Control Inter-face Protocol Waveform shows an example of this protocol for the GHI (Get Header from ISAMx) and GST (Get Status Register) instructions.

The bus width and clock rate of the control interface has been carefully matched to the internal bandwidth of the Switching Memory, and to the control requirements for high-speed multiport traffic. Additionally, many of the commands which require multiple SCLK cycles to execute, allow other commands to overlap the command cycles. In this manner, the commands can be pipelined. The control interface of the Switching Memory provides sufficient bandwidth to keep pace with the control operations required of all sixteen data ports, the memory refresh activities, and the other associated overhead.

#### **Control Interface Commands**

|                      |                                                                  | COMMAND Bus Bit (CMD5:0)<br>MSb LSb |   |   |                |                |                |  |

|----------------------|------------------------------------------------------------------|-------------------------------------|---|---|----------------|----------------|----------------|--|

| Command <sup>1</sup> | Command Description                                              | 5                                   | 4 | 3 | 2              | 1              | 0              |  |

| GPIx                 | Get Pre/Post Pend Data from ISAMx <sup>2</sup>                   | 0                                   | 0 | 0 | n <sup>3</sup> | n <sup>3</sup> | n <sup>3</sup> |  |

| GHIx                 | Get Header from ISAMx <sup>2</sup>                               | 0                                   | 0 | 1 | n <sup>3</sup> | n <sup>3</sup> | n <sup>3</sup> |  |

| GPE                  | Get Pre/Post Pend Data from Edit Buffer                          | 0                                   | 1 | 0 | 0              | 0              | 0              |  |

| GHE                  | Get Header from Edit Buffer                                      | 0                                   | 1 | 0 | 1              | 0              | 0              |  |

| GST                  | Get ISAM and OSAM Status Register Bits                           | 0                                   | 1 | 0 | 0              | 1              | 0              |  |

| GER                  | Get Error Register Bits                                          | 0                                   | 1 | 0 | 1              | 1              | 0              |  |

| STEx                 | Store Cell in ISAMx <sup>2</sup> and Input Edit Buffer in Memory | 1                                   | 0 | 0 | n <sup>3</sup> | n <sup>3</sup> | n <sup>3</sup> |  |

| STIx                 | Store Cell in ISAMx <sup>2</sup> in Memory                       | 1                                   | 0 | 1 | n <sup>3</sup> | n <sup>3</sup> | n <sup>3</sup> |  |

| LDOx                 | Load Cell from Memory into OSAMx <sup>2</sup>                    | 1                                   | 1 | 0 | n <sup>3</sup> | n <sup>3</sup> | n <sup>3</sup> |  |

| PPE                  | Put new Pre/Post Pend in Input Edit Buffer                       | 1                                   | 1 | 1 | 0              | 0              | 0              |  |

| PHE                  | Put new Header in Input Edit Buffer                              | 1                                   | 1 | 1 | 1              | 0              | 0              |  |

| PHEC                 | Put new Header and new CRC byte in Input Edit Buffer             | 1                                   | 1 | 1 | 1              | 0              | 1              |  |

| REF                  | Refresh Memory                                                   | 0                                   | 1 | 0 | 1              | 1              | 1              |  |

| LDC                  | Load Configuration Register                                      | 1                                   | 1 | 1 | 0              | 1              | 0              |  |

| OPE                  | Put Pre/Post Pend Data in Output Edit Register                   | 1                                   | 1 | 1 | 0              | 1              | 1              |  |

| OHE                  | Put new Header in Output Edit Register                           | 1                                   | 1 | 1 | 1              | 1              | 0              |  |

| OHEC                 | Put new Header and new CRC byte in Output Edit Register          | 1                                   | 1 | 1 | 0              | 0              | 1              |  |

| NOP                  | No Operation                                                     | 1                                   | 1 | 1 | 1              | 1              | 1              |  |

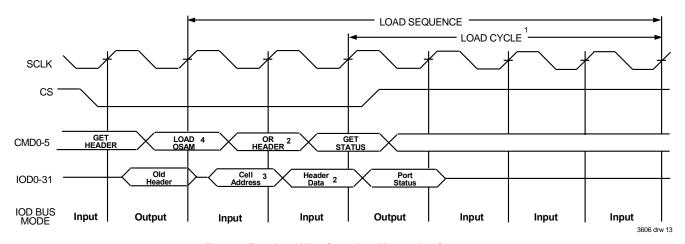

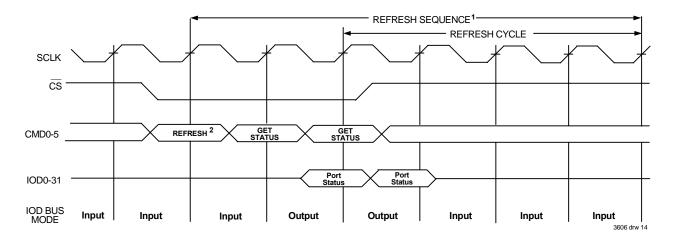

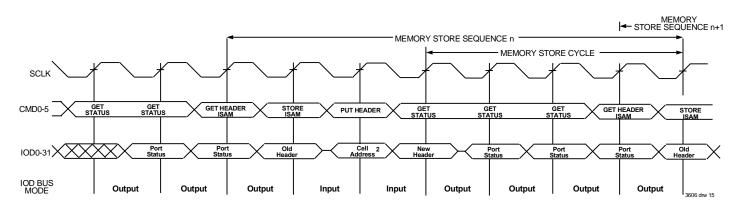

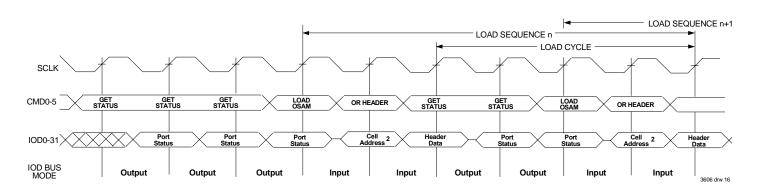

## **Control Interface Timing Waveform**

CTLEN is Low and the CTLEN bit of the configuration register (Bit 31) is LOW for this waveform.

<sup>&</sup>lt;sup>1</sup>All output signals except CRCERR are controlled by OE.

<sup>1.</sup> CMD bus commands not defined in this table are undefined and not to be implemented.

2. "x" represents the specific ISAM or OSAM being accessed (IP0-IP7 or OP0-OP7 respectively).

<sup>3. &</sup>quot;n" represents the appropriate bit of the binary representation of the ISAM or OSAM being accessed (000 to 111).

<sup>&</sup>lt;sup>2</sup>The 13-bit cell address, 4-bit selected Switching Memory address, and the 5-bit Edit Buffer Protect and Clear control bits are valid at this time.

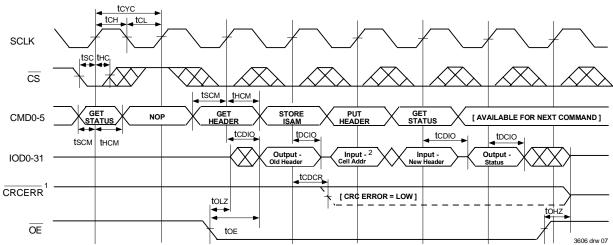

## **Control Enable Timing Waveform**

The CTLEN bit of the configuration register (Bit 31) is LOW for this waveform. If the CTLEN bit of the configuration register is set HIGH at device initialization the IOD bus will always be in input mode for multiple Switching Memory configurations.

#### **Reset Waveform**

Reset function can also be accomplished by holding the RESET bit [Bit 30] High on the IOD bus during a LDC (Load Configuration Register) command.

<sup>&</sup>lt;sup>1</sup>tRST must be greater than two SCLK cycles. Any glitch could cause an erroneous reset operation.

### **Input Port Timing Waveform**

<sup>1</sup>ICLK frequency must not exceed the SCLK frequency.

## **Output Port Timing Waveform**

<sup>&</sup>lt;sup>1</sup>OFRMx is actually tri-stated by the device one cycle before the end of the frame; the logic Low level is due to the recommended 5k ohm resistor on the OFRMx line.

<sup>&</sup>lt;sup>2</sup>RESET must be Low 10ns prior to the next rising SCLK edge to insure that the Reset function is not repeated

<sup>&</sup>lt;sup>2</sup>tSIF and tHIF (IFRM Setup and Hold) must be met for each ICLK rising edge for IFRM Low and High.

#### **Input Ports**

A 155Mbps input Data Path Interface (DPI) consists of six pins – four data bits (IPxD0-3), an input clock (ICLKx), and an input framing signal (IFRMx). A further definition of the DPI interface is available in Technical Note 34, available on the IDT Web Site (www.idt.com). The "x" in the signal name corresponds to a port number (0 through 7 for the 8 x 8 port configuration). IPxD0-3 and IFRMx are synchronous inputs with respect to the rising edge of ICLKx, and the ICLK frequency must not exceed the SCLK frequency. Each Input SAM (ISAMx) is double buffered, with each ISAM buffer able to store a single ATM cell of up to 56 bytes in length. The 32-bit Header and up to 32 bits of Pre-Pend and/or Post-Pend bytes may be accessed and modified via the Control Data Bus interface.

The Input Port Timing Waveform assumes that the Switching Memory has been initialized and the ISAMs are empty. An active HIGH IFRMx signal indicates that the first nibble of a new cell will be received on the next rising edge of ICLKx and the cell counter is initialized. Data will be sequentially clocked into the ISAM buffer on each subsequent ICLKx rising edge after IFRMx goes LOW. The status register bit indicating ISAMx buffer is full will be set HIGH when the ISAM counter reaches the stop address. The ISAM start and stop address is programmed via the configuration register at initialization to establish the input cell length and protocol. If IFRMx input goes HIGH before the stop position address is reached, the start byte position address will be reloaded, the ISAM Full Status indicator will not be set, a Short Cell error status indicator will be set in the error register, and the cells will be overwritten. If the IFRMx does not go HIGH when the stop position address is reached, the ISAM Full status indicator and a Long Cell error status indicator will be set. A Long Cell error results in the beginning portion of the long cell being kept, the last portion being discarded, and the next cell being accepted in the other half of the ISAM on the next IFRMx HIGH. When the IFRMx input stays HIGH, the load start byte position address process will repeat for every ICLKx and the actual count will not start until IFRMx goes LOW. A subsequent cell may be input back-toback (no dead cycle on the IOD bus). In this case the IFRMx of the second cell will occur on the same ICLKx rising edge as the last data nibble of the first cell.

When the control logic returns 32-bits of information across the IOD bus during a STORE command, the five most significant bits provide the Byte Edit control for the first word of the input edit buffer. These four bytes are either cleared, protected, or unaffected depending on the value of the bits IOD27-31. These five bits are updated each time a STORE command is executed. IOD31 determines if the function is clear or protect; IOD 27-30 select which bytes in the first word of the Input edit buffer are affected. The Edit Buffer Protect/Clear Codes table defines the possible combination of these bits.

Each of the eight 4-bit input ports is capable of receiving 155Mbps data; however, the ports can be combined in groups of four bits to receive data rates up to 1.2Gbps. For example, four 4-bit ports can be combined to receive 622Mbps traffic. The output ports can also be combined, via the configuration register, independent of the input data ports. This allows the Switching Memory to be configured as a concentrator, expander, or cell buffer with multiple bus widths. When combining

ports, the chip is internally reconfigured to accept a single master ICLK for the grouped ports (always using the least significant ICLK/IFRM of those combined), and the data path is internally switched to correctly align the ports for CRC generation and Header/Pre-Post Pend comparison. See the Port Configuration Code Table for option definitions. By varying the input and output port options, one hundred different port configurations are available to the user to optimize design flexibility.

#### **Output Ports**

The output data ports are similar in operation to the input data ports. There are eight 155Mbps DPI ports, six pins each. Data is transmitted out the 4-bit data bus (OPxD0-3), synchronous with the output clock (OCLKx). An output framing signal (OFRMx) is provided which is also synchronous with respect to OCLKx.

The output port protocol was designed to interface directly with the input port of another Switching Memory without requiring additional logic. This allows cascading of multiple Switching Memory chips to implement wider multiplexers or larger capacity cell buffers without additional logic. To facilitate cascading, OFRMx has been implemented as a tri-statable I/O, while OPxD pins are tri-statable outputs. All chip outputs can be disabled to a high impedance state by asserting the  $\overline{\text{OE}}$  pin HIGH.

Output ports of a single device or of multiple devices may share an output bus if they are configured in the cell bus mode, where control logic performs the arbitration between IDT77V400s, or are externally controlled via the OE. In the cell bus mode configuration, one external controller would typically drive the control interface of multiple Switching Memory chips and use the OFRMx to arbitrate the shared bus.

Output SAM (OSAMx) control logic must receive a LDx (Load OSAMx) instruction from the external controller via the Command Bus to dispatch a cell. The LDx instruction initiates a cell transfer from the memory location specified on the IOD Bus to the specified OSAMx. At this point the user has the option of modifying the Header and the Pre-Post Pend bytes. When the output buffer has a cell loaded to send, Switching Memory will immediately assert the specific OFRMx HIGH for one OCLKx cycle prior to transmitting data. When the OFRMx is then asserted LOW, the first data nibble of the new cell will appear prior to the next rising edge of OCLKx. The output port will continue to assert OFRMx LOW (while the cell is output from OSAMx) for a minimum of two cycles before the end of the cell transmission. At that time (if in cell bus mode) OFRMx is released to a high-impedance state during the cycle before the end of the frame to allow collision free control transfer to another Switching Memory. After asserting OFRMx HIGH, the OSAMx EMPTY bit in the status register will be set, indicating that an OSAM buffer is available for a new cell to be loaded from the memory. The EMPTY bit is reset when a LDx command is performed and after the cell is transmitted. It is recommended that a pull down resistor be used on OFRMx pin to eliminate the possibility of an invalid OFRMx HIGH. The value of this pull down resistor will be determined by a specific board design or noise issues. A  $5K\Omega$  resistor is recommended for this pull down function, although 50-100K $\Omega$  may be sufficient in most applications.